第二節(jié) 8086系統(tǒng)組成

8086是一種微處理器,再加上必須的支持芯片,如時鐘發(fā)生器,地址鎖存器,總線驅(qū)動器 ,存儲器和I/O接口等,才能構(gòu)成一臺完整的微型計(jì)算機(jī).根據(jù)外部設(shè)備的數(shù)量和系統(tǒng)復(fù)雜 程度,8086可以選用兩種系統(tǒng)構(gòu)成模式,最小模式和最大模式.最小模式是單CPU系統(tǒng),在 這種系統(tǒng)中,8086的MN/MX引腳接高電平,系統(tǒng)全部的控制信號都直接由CPU提供.最大模式 是多CPU系統(tǒng),此時MN/MX引腳接低電平,必須通過8288總線控制器對CPU的狀態(tài)信息進(jìn)行 譯碼才能產(chǎn)生系統(tǒng)必須的控制信號.

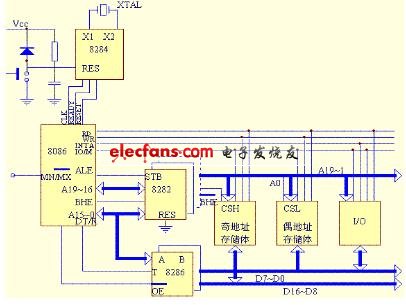

最小模式系統(tǒng)構(gòu)成如圖7-9所示.這時8086的MN/MX引腳接至VCC,它直接產(chǎn)生存儲器 和I/O端口的讀寫命令,如IO/M,RD,WR,INTA,直接產(chǎn)生地址鎖定信號ALE,控制數(shù)據(jù)收發(fā)器 的控制信號DT/R,DEN.

1.地址鎖存

8086的AD15~~AD0是地址/數(shù)據(jù)復(fù)用線,即CPU與存儲器進(jìn)行信息交換時,首先在T1 狀態(tài),先由CPU送出訪問存儲單元的地址信息到AD15~~AD0上,隨后又用在些線來傳送數(shù)據(jù) 所以在數(shù)據(jù)送上總線以前,必須先將地址鎖存起來.可用8282或74LS373鎖存8086的單向 地址AD15~~AD0.圖7-9中使用三片8282,這是因?yàn)?282只具有8位鎖存功能,而8086具有 20位地址和一根BHE信號.若系統(tǒng)存儲器容量較小,使用不到20位地址信息,也可只用2 片8282.圖中OE端接地,使鎖存器永遠(yuǎn)處于允許輸出狀態(tài).引腳STB接8086的ALE輸出.在 總線周期T1狀態(tài),ALE上出現(xiàn)正脈沖,它的下降沿將8282輸入端的地址信息存入鎖存器, 并由輸出端送入地址總線.

2.雙向數(shù)據(jù)總線驅(qū)動器

CPU可以直接將數(shù)據(jù)發(fā)送到數(shù)據(jù)總線上.而無需鎖存.為了增加總線負(fù)載能力,CPU數(shù)據(jù) 總線一般要加上驅(qū)動器,且要求雙向驅(qū)動器,一般采用8位雙向驅(qū)動器8286或74LS245.由于 8086數(shù)據(jù)總線是16位的,所以要用2片8286.8286的Ai引腳接CPU的ADi,其Di引腳接到系統(tǒng) 數(shù)據(jù)總線D1上,并將8086的DT/R接8286的T引腳,當(dāng)DT/R為高電平時,數(shù)據(jù)從CPU發(fā)送到數(shù)據(jù) 總線上.DT/R為低電平時,CPU從數(shù)據(jù)總線上接收數(shù)據(jù).8286的OE腳接8086的DEN腳.當(dāng)8086 的DEN為低電平時,才允許數(shù)據(jù)輸入或輸出.

3.時鐘發(fā)生器/驅(qū)動器

8086所需時鐘脈沖CLK由8284提供.8284輸出時鐘CLK的頻率,取決X1,X2跨接石英晶體的 頻率.除此以外,8284還向8086提供定時和寬度符合要求的RESET復(fù)位信號及符合要求的 READY信號.

4.存儲器部件

8086能直接尋址1MB存儲空間.這個存儲空間分為兩個512KB存儲體.一個存儲體由奇地址 單元組成,用于存儲16數(shù)據(jù)的高字節(jié),另一個存儲體由偶地址單元組成,用于存儲16位 數(shù)據(jù)低字節(jié).前者稱為奇地址存儲器,后者稱為偶地址存儲體.偶地址存儲體的8位數(shù)據(jù) 總線接CPU的數(shù)據(jù)總線D7~~D0,而奇地址存儲體8位數(shù)據(jù)線接數(shù)據(jù)總線D15~~D8.地址線A19 ~~A1同時接到兩個存儲體,而A0作為偶地址選中信號即A0=0時,選中偶存儲體.BHE作為 奇地址片選信號,BHE=0時選中奇存儲體.所以兩個存儲體可以同時讀出或?qū)懭?也可單獨(dú) 選中一個存儲體.

5.I/O端口

一個完整的微機(jī)系統(tǒng)必須有I/O設(shè)備.I/O設(shè)備都有端口地址號.CPU通過地址總線發(fā)出端口 地址,經(jīng)過端口地址譯碼器輸出,送到端口的片選引腳而選定指定的端口.8086根據(jù)執(zhí)行 命令是訪問存儲器指令還是輸入輸出指令,來使M/IO控制信號是高電平或是低電平,以 區(qū)分地址總線上的地址是訪問存儲器還是訪問外設(shè).

以8086為CPU的單CPU系統(tǒng),數(shù)據(jù)總線是8位的,所以只用一片8286.存儲器也不分 奇偶存儲體.而只有一個以字節(jié)為單位的存儲體.其它與8086系統(tǒng)構(gòu)成相同.

§2.2 最大模式系統(tǒng)的構(gòu)成

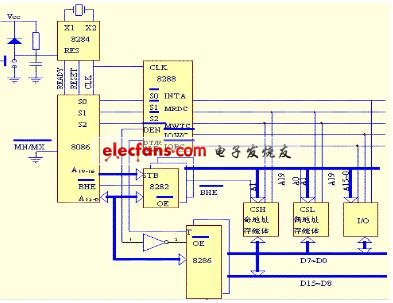

最大模式的8286系統(tǒng)結(jié)構(gòu)如圖7-10所示.在這種系統(tǒng)中,是將MN/MX接地,并采用8288 總線控制器來提供下列控制號:MRDC,MWTC,IORC,IOWC,INTA,DEN,DT/R和ALE等.

§2.3 IBM PC/XT微機(jī)系統(tǒng)的組成

IBM PC/XT微機(jī)是以8086為CPU的最大模式系統(tǒng),以此為例進(jìn)一步了解各支持芯片功能.

1.IBM PC/XT子系統(tǒng)

IBM PC/XT CPU子系統(tǒng)控制電路如圖7-11所示,它由下列芯片組成:8088CPU,8087 協(xié)處理器插座(是否擦入可任選),8284時鐘發(fā)生器,74LS245雙向總線驅(qū)動器,74LS373 地址鎖存器和74LS244地址驅(qū)動器.8088的MN/MX接地,它工作于最大模式,8288的IOB接 地,它工作于系統(tǒng)總線模式.

(1)8284的作用及連接 8284向系統(tǒng)提供CLK,PCLK和OSC三種頻率時鐘信號及復(fù)位 信號RESET,準(zhǔn)備好信號READY.

8284的X1與X2間接頻率為14.31818MHZ的晶體振蕩器,因此CLK的頻率為4.77MHZ, 占空比為33%,它作為8288,8088,8087的主時鐘.PCLK是CLK的二分頻,它的頻率為2.385MHZ ,占空比為50%,OSC是14.31818MHZ,OSC和PCLK送到I/O插槽上供外圍部件使用.

8284的RES輸入引腳接PWRGOOD信號,PWRGOOD是電源好信號,當(dāng)系統(tǒng)加電時,若系統(tǒng) 電源正負(fù)5V,正負(fù)12V四種直流電壓均正常后,由于RC網(wǎng)絡(luò)的作用會在PWRGOOD引腳上出現(xiàn) 50微法的負(fù)脈沖,它經(jīng)8284整形后,由CLK的下降沿打入同步觸發(fā)器FF2,在FF2的Q端輸出 系統(tǒng)復(fù)位信號RESET,該信號送到8088和8087及系統(tǒng)其它部件作為復(fù)位信號.

8284的RDY1引腳接至DMA控制電路的等待請求信號DMAWAIT上,AEN1腳接到系統(tǒng)等待控制電路RDY/WAIT信號上.當(dāng)DMAWAIT為高電平和RDY/WATI為低電平時,8284的READY輸出 高電平,該信號與8088和8087的READY腳相連.根據(jù)8088和8087規(guī)定,當(dāng)他們在T2上升沿 采樣到READY信號為低電平時,就會在T2之后插入TW狀態(tài),并在每個TW開始的上升沿繼續(xù) 采樣READY信號.若READY還是低電平,則繼續(xù)插入TW狀態(tài),直到READY引腳為高電平為止 CPU脫離等待狀態(tài),執(zhí)行后續(xù)有關(guān)操作周期.

(2)地址和數(shù)據(jù)接口部件 地址鎖存器由兩個74LS373(U5,U7)和一個74LS244(U6) 組成.U7鎖存A19~~A12,U5鎖存A7~~A0,A11~~A8在CPU總線周期不發(fā)生變化,不需鎖存,僅 用U6增大驅(qū)動能力.

U5和U7的控制端G接8288的ALE信號,在ALE的下降沿將其鎖住.而OE腳和U6的1G腳受AENBRED信號控制.808和8087控制系統(tǒng)總線時,AENBRD為低電平,U5,U7和 U6允許輸出.即把20位地址信息A19~~A0送上地址總線.U2是雙向總線驅(qū)動器,8288的輸出 DEN反相后接到U2的允許端G,在8088或8087控制總線時,DEN為高電平,G為低電平,使CPU 數(shù)據(jù)總線與系統(tǒng)總線和相通.8288的DT/R信號接到U2的方向控制端DIR,由它控制數(shù)據(jù)傳送方向.

(3)8288的連接作用 因?yàn)橄到y(tǒng)工作于最大模式,必須使用8288.系統(tǒng)控制信號是 8288對8088或8087的S2,S1,S0狀態(tài)信息進(jìn)行譯碼后產(chǎn)生的.所以8088和8087的S2,S1,S0 腳分別接到8288的相應(yīng)引腳上.8288的IOB腳接地,工作于系統(tǒng)總線模式.8288的AEN腳, 接到DMA應(yīng)答電路的AENBRD信號上,而將CEN引腳接到同一電路的AEN上,當(dāng)8088控制總線 時,AENBRD為低電平,而AEN為高電平,8288能對8088送來的狀態(tài)信息譯碼,產(chǎn)生各種命令 信號,這些信號送到系統(tǒng)總線的接口部件,控制相應(yīng)的動作.反之,當(dāng)DMA控制系統(tǒng)總線時, AENBRD為高電平,禁止8288工作,8288輸出均為高阻狀態(tài),同時應(yīng)答電路送出AEN信號為 低電平,使8288輸出的控制信號DEN,DT/R和ALE等均無效,使雙向驅(qū)動器和數(shù)據(jù)總線脫離, 并封鎖地址鎖存器,此時由DMA控制系統(tǒng)總線.

(4)8087的連結(jié) 8087是協(xié)處理器,是專門進(jìn)行浮點(diǎn)運(yùn)算的處理器,插上8087可大大 提高IBM PC/XT的運(yùn)算速度.由圖7--11可見,具有8087的系統(tǒng),除增加8087芯片外,并不需 增加其他邏輯電路,它與8088功用時鐘電路8288,共用一套接口部件,只需將8088的QS1,QS0與8087的QS01,QS0相連,8087的BUSY接8088的TEST腳即可.

2.I BM PX/XT的等待控制電路

在IBM PC/XT系統(tǒng)板上,有控制準(zhǔn)備好信號的等待控制電路.該電路的任務(wù)是:當(dāng)8088 或8237DMA控制器在總線訪問周期需用插入等待狀態(tài)時,能分別向他們各自的READY引腳 送出低電平信號,以達(dá)到在總線周期插入等待狀態(tài)的目的.

(1)IBM PC/XT需要插入等待狀態(tài)的情況 8088的基本總線周期為四個時鐘周期, 一般情況下,CPU與存儲器是相匹配的,讀寫周期為4個T,訪問I/O設(shè)備為5個T.8237DMA控制 器控制總線時,通道0用于動態(tài)存儲器刷新需要4個T,通道1~~3用于存儲器與I/O設(shè)備之間 傳送,每個DMA傳送周期為5個T.當(dāng)與總線相連的設(shè)備數(shù)據(jù)傳送速度比總線要求的速度慢時 為了不丟失數(shù)據(jù),可讓設(shè)備選中時發(fā)出等待信號申請,啟動等待控制電路,插入需要的若干 個等待信號.

(2)等待控制電路組成 圖7--12是PC/XT的等待控制電路,它由兩個D觸發(fā)器和一些 門電路組成.正常工作時,兩個觸發(fā)器均處于0狀態(tài),輸出信號RDY/WAIT為低電平,RDY TO DMA為高電平.此時等待電路不起作用.為了啟動等待控制電路,可以加兩類啟動信號:

將I/OCHRDY信號變低,使觸發(fā)器U70置1,而使RDY/WAIT變高,RDY TO DMA信號變低, 使8088或8237DMA的READY信號變低,在T2之后插入TW狀態(tài),一直持續(xù)到I/O CHRDY信號為 高電平為止.所以當(dāng)與系統(tǒng)總線連結(jié)的設(shè)備速度與8088或8237不匹配時,就在系統(tǒng)選中 該設(shè)備時,自動啟動等待電路,產(chǎn)生低電平的I/O CHRDY信號.

在U70的11腳產(chǎn)生CP觸發(fā)脈沖,使U70置1,產(chǎn)生這個脈沖的條件是:8088處在I/O讀或?qū)懼芷谥?IOR或IOW爲(wèi)負(fù)跳變信號,非動態(tài)RAM刷新的DMA操作(DACK0BRD,AENBRD,MEMR). 這些條件任一個滿足,就把U70置1,使RDY/WAIT為高電平,在下一個時鐘到來時,把U88 置1,它一方面輸出低電平的RDY TO DMA,另一方面使U70置0,RDY/WAIT又恢復(fù)低電平,再 下一個時鐘,又只U88置0.RDY/WAIT信號輸入至8284的AEN1,通過8284使8088插入一個等待 狀態(tài),RDY TO DMA信號送至8237DMA,使它在DMA傳送周期中插入一個等待狀態(tài).

(3)I/O寫時序分析 圖7--13是I/O寫周期插入等待狀態(tài)時序.I/O寫時序共用5個 時鐘周期(T1,T2,T3,TW,T4),下面分析TW的插入過程.

系統(tǒng)復(fù)位后,任一總線周期開始之前,U70或U88都處于0狀態(tài),即RDY/WAIT為低電平 ,而RDY TO MDA為高電平.

在T1狀態(tài)結(jié)束的下降沿,寫信號IOW變?yōu)橛行У牡碗娖?經(jīng)U72反相,產(chǎn)生U70觸發(fā)器 的觸發(fā)脈沖,使U70變?yōu)?狀態(tài),RDY/WAIT變?yōu)楦唠娖?而RDY TO DMA變?yōu)榈碗娖?RDY/WAIT信號接到8284的AEN1引腳.圖7--13看出,在T2的下降沿使8284的READY輸出低電平.雖然RDY TO DMA接DMA控制器8237的READY引腳,但因CPU控制著總線,此信號無效.

T2的上升沿,使U88變?yōu)?,它的Q端接到U70的R端,使U70變?yōu)?狀態(tài),使RDY/WAIT爲(wèi)低電平,即8284的AEN1變?yōu)榈碗娖?但由于8284的ASYNC接低電平,所以它的READY引腳要經(jīng)過T3的上升沿和下降沿后,才會變?yōu)榈碗娖?

T3的上升沿,CPU采樣自己的READY引腳,若為低電平,就在T3結(jié)束時,插入一個TW狀態(tài),同時T3的上升沿將U88清零,使RDY TO DMA變?yōu)楦唠娖?

在TW的上升沿,CPU又去采樣自己的READY引腳,此時READY已經(jīng)是高電平了,所以CPU 結(jié)束等待狀態(tài),進(jìn)入T4狀態(tài),結(jié)束I/O寫周期.