第三節(jié) 多處理器結(jié)構(gòu)

在計算機(jī)系統(tǒng)中,具有兩個或兩個以上同時執(zhí)行指令的部件稱為多處理器結(jié)構(gòu).增加的處理器可以是專用處理器,如IBM PC/XT中用的協(xié)處理器8087是專門用來進(jìn)行浮點運算的 也有的是通用處理器.隨著單片微處理器性能價格比提高,使用多處理器比使用集中控制 式單個處理器更為經(jīng)濟(jì)有效,且應(yīng)用靈活,宜于分成模塊結(jié)構(gòu),便于擴(kuò)充或維修.

8088的最大模式是專為實現(xiàn)多處理器而設(shè)計的.最大模式提供的多個處理性能適合于三種基本配置:協(xié)處理器配置,緊耦合配置和松耦合配置.前兩種配置十分相似,二者的CPU和支持處理器不僅共享整個存儲器和I/O子系統(tǒng),而且還共享同一個總線控制邏輯和 時鐘發(fā)生器,這這兩種配置中,8086為主控處理器,支持處理器為從處理器,由主CPU提供 總線訪問和控制,支持處理器向CPU發(fā)出總線請求信號.緊耦合配置中,支持處理器可以 獨立的工作,但協(xié)處理器不能獨立操作,必須直接與CPU通信.圖7--14是緊耦合配置圖.

松耦合配置用于中型和大型系統(tǒng)中,系統(tǒng)中每個模塊都可以作為系統(tǒng)總線的主控設(shè)備幾個模塊可共享系統(tǒng)資源,而系統(tǒng)總線控制邏輯必須解決總線爭用問題.處理器的通信可通過共享資源來實現(xiàn).同時每個模塊還可以有自己的存儲器和I/O設(shè)備.

§7.3.1 協(xié)處理器配置

雖然8086CPU功能很強(qiáng),但其指令系統(tǒng)不能有效的滿足某些復(fù)雜應(yīng)用的要求.在這種應(yīng)用 中,配上協(xié)處理器,以便擴(kuò)充指令系統(tǒng)完成特殊的計算任務(wù),如協(xié)處理器8087就能快速實現(xiàn) 浮點運算.協(xié)處理器配置只需8086工作在最大模式,不需要增添其他邏輯,CPU和協(xié)處理器 都執(zhí)行同一個用8086擴(kuò)充指令系統(tǒng)編寫的程序.若指令由協(xié)處理器執(zhí)行,則CPU除了可能 要為協(xié)處理器取出操作數(shù)之外,并不需執(zhí)行其它操作.

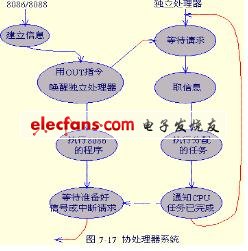

協(xié)處理器執(zhí)行指令時,CPU和協(xié)處理器之間的相互作用如圖7--16所示.系統(tǒng)在執(zhí)行程序 時,只有主CPU能取指令,協(xié)處理器能夠接收所有指令并監(jiān)視主CPU指令執(zhí)行過程.主CPU 在執(zhí)行程序時,若需要協(xié)處理器工作,程序中安排一條交權(quán)指令ESC,該指令喚醒協(xié)處理器 并告訴協(xié)處理器必須執(zhí)行的操作和運算.主CPU和協(xié)處理器同時對該指令譯碼,此時主CPU 可能轉(zhuǎn)到執(zhí)行下一條指令,或者為協(xié)處理器讀取存儲器操作數(shù)的第一個字,而協(xié)處理器向 主CPU發(fā)高電平信號(忙)到TEST引腳,并執(zhí)行指定的操作,二者并行工作.若主CPU需要協(xié) 處理器操作結(jié)束,或者讓協(xié)處理器完成另外的操作,主CPU要反復(fù)執(zhí)行等待指令,當(dāng)協(xié)處 理器完成操作后,向主CPU發(fā)低電平信號到TEST引腳,主CPU就可順序執(zhí)行后序指令.協(xié)處理 器和主CPU的連接圖見圖7--17,它們共享同一個時鐘發(fā)生器和總線控制器.協(xié)處理器必須 具有如下功能:

(1)當(dāng)ESC指令在譯碼和和執(zhí)行期間發(fā)生錯誤時,它將發(fā)出中斷請求信號.

(2)當(dāng)附加的數(shù)據(jù)必須從存儲器中讀出或?qū)懭霑r,協(xié)處理器能通過主CPU的RQ/GT引腳 發(fā)出總線請求,以竊取總線周期.

(3)當(dāng)協(xié)處理器忙時,它必須給主CPU的TEST引腳發(fā)出一個高電平信號.

§7.3.2 緊耦合系統(tǒng)

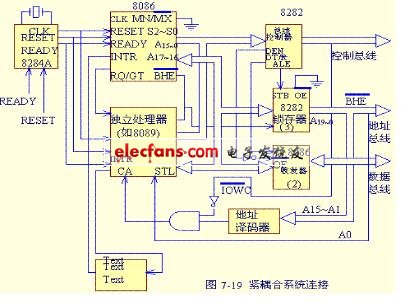

8086還可以和獨立的處理器連接,形成進(jìn)耦合多處理器系統(tǒng).在這個系統(tǒng)中CPU和獨立 處理器共享同一個時鐘發(fā)生器和總線控制邏輯.獨立處理器要取指令或者數(shù)據(jù),向CPU的 RQ/GT引腳請求總線訪問.主COPU和獨立處理器工作過程如圖7--18所示.相互之間通信是 通過共享存儲空間實現(xiàn)的.主CPU在存儲器為獨立處理器準(zhǔn)備一個描述待執(zhí)行任務(wù)的控制 塊然后用輸出指令把任務(wù)分配給獨立處理器.獨立處理器從共享存儲器得到任務(wù)和程序 入口地址并執(zhí)行用自己的指令系統(tǒng)編寫的程序.與主CPU并行工作,獨立完成任務(wù).任務(wù) 完成后,獨立處理器向主CPU發(fā)中斷請求或修改存儲器的狀態(tài)單元的內(nèi)容,通知主CPU.

圖7-19給出8086COPU與獨立處理器8089組成的緊耦合系統(tǒng).它們共享總線,當(dāng)一個處理器在使用總線時,其它的處理器的總線位于高阻狀態(tài).獨立處理器通過主CPU的RQ/GT 引腳請求總線.為了喚醒獨立處理器,主CPOU要執(zhí)行一條輸出指令,指令的端口地址分配 給獨立處理器的一個端口.

§7.3.3 松耦合系統(tǒng)

松耦合系統(tǒng)中,每個CPU有自己的總線控制邏輯部件,總線裁決通過擴(kuò)展總線控制邏輯和 增加外部邏輯電路來解決,并且這部分邏輯電路對所有模塊是公用的.幾個CPU能形成 一個很大系統(tǒng),每個COPU還可接協(xié)處理器或獨立處理器.松耦合系統(tǒng)有以下優(yōu)點:

(1)系統(tǒng)吞吐量高.

(2)系統(tǒng)可按模塊形式設(shè)計,每個總線主控模塊是一個獨立的部件,擴(kuò)充方便.

(3)一個模塊出故障不會破壞整個系統(tǒng),易于檢查或維修.

(4)每一個總線主控設(shè)備可以有局部總線,用于訪問專用的存儲器和I/O設(shè)備,這樣可 進(jìn)一步提高并行處理能力.

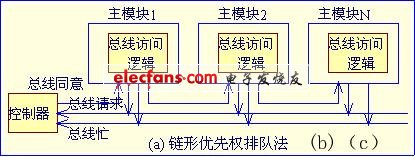

松耦合系統(tǒng)中,多個總線主控模塊能訪問共享的系統(tǒng)總線,由于每一個主控模塊獨立 運行,必須增加控制電路解決總線裁決問題.這種電路稱為總線訪問邏輯部件,它的職責(zé) 是確保在某一時刻只有一個總線主控設(shè)備控制系統(tǒng)總線,同時發(fā)生的總線請求根據(jù)優(yōu)先權(quán) 來解 決.圖7--20是三種優(yōu)先級排隊方法連結(jié)圖.它們是鏈形排隊法,查詢法和獨立請求法.

鏈?zhǔn)絻?yōu)先權(quán)排隊法中所有的主控模塊用同一條線請求總線,若總線不忙,則控制器 發(fā)出總線同意信號以響應(yīng)總線請求.同意信號串行的通過每個主控模塊,直到它遇到請求 訪問的另一個主控模塊為止,這個模塊阻止了總線同意信號往下傳送,使忙線有效.所以 離控制器最近的模塊優(yōu)先權(quán)高.這種方法簡單,成本低,但速度慢.

查詢法也使用一條請求線,當(dāng)控制器響應(yīng)請求時,產(chǎn)生一系列模塊地址到地址編碼線 當(dāng)提請求的模塊識別到的地址時,激勵忙線,并開始使用總線.

獨立請求法是并行方法解決優(yōu)先權(quán)問題.每個模塊有一個總線請求和同意線,且分配 給一定優(yōu)先權(quán),控制器有一個優(yōu)先權(quán)譯碼器,它選擇具有最高優(yōu)先權(quán)的請求并返回相應(yīng) 同意信號,這種方法速度快.INTEL8289總線裁決器是專門為提供總線聯(lián)絡(luò)訪問信號而設(shè)計的.