BJ-EPM240學(xué)習(xí)板:MAX II內(nèi)部震動(dòng)時(shí)鐘使用實(shí)驗(yàn)

采用CPLD市場領(lǐng)先供應(yīng)商提供的MAX? II 開發(fā)套件,您可以評估MAX II CPLD的系列特性....

BJ-EPM240學(xué)習(xí)板:乘法器設(shè)計(jì)實(shí)驗(yàn)

乘法器是模擬式電子式電能表的重要組成部分,也是電能表計(jì)量誤差的最主要來源。對時(shí)分割乘法器在諧波條件下....

BJ-EPM240學(xué)習(xí)板:VGA接口實(shí)驗(yàn)

VGA接口就是顯卡上輸出模擬信號的接口,VGA(Video Graphics Array)接口,也叫....

BJ-EPM240學(xué)習(xí)板:Johnson計(jì)數(shù)器實(shí)驗(yàn)

在數(shù)字電子技術(shù)中應(yīng)用的最多的時(shí)序邏輯電路。計(jì)數(shù)器不僅能用于對時(shí)鐘脈沖計(jì)數(shù),還可以用于分頻、定時(shí)、產(chǎn)生....

BJ-EPM240學(xué)習(xí)板:數(shù)碼管顯示實(shí)驗(yàn)

數(shù)碼管要正常顯示,就要用驅(qū)動(dòng)電路來驅(qū)動(dòng)數(shù)碼管的各個(gè)段碼,從而顯示出我們要的數(shù)字,因此根據(jù)數(shù)碼管的驅(qū)動(dòng)....

課程3:FPGA開發(fā)流程概述

FPGA利用小型查找表(16×1RAM)來實(shí)現(xiàn)組合邏輯,每個(gè)查找表連接到一個(gè)D觸發(fā)器的輸入端,觸發(fā)器....

BJ-EPM240學(xué)習(xí)板:按鍵消抖實(shí)驗(yàn)

按鍵消抖通常的按鍵所用開關(guān)為機(jī)械彈性開關(guān),當(dāng)機(jī)械觸點(diǎn)斷開、閉合時(shí),由于機(jī)械觸點(diǎn)的彈性作用,一個(gè)按鍵開....

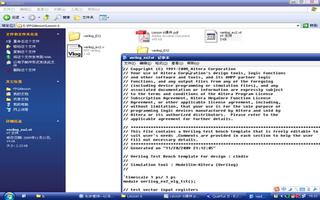

課程4:Verilog語法基礎(chǔ)

Verilog HDL是一種硬件描述語言,用于從算法級、門級到開關(guān)級的多種抽象設(shè)計(jì)層次的數(shù)字系統(tǒng)建模....

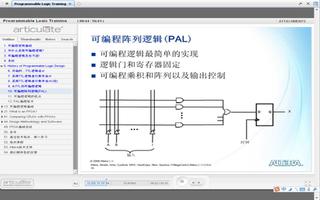

FPGA教程:可編輯邏輯器件基礎(chǔ)

PLD與一般數(shù)字芯片不同的是:PLD內(nèi)部的數(shù)字電路可以在出廠后才規(guī)劃決定,有些類型的PLD也允許在規(guī)....

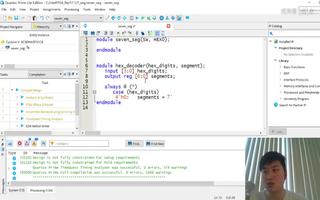

FPGA Verilog實(shí)現(xiàn)4位數(shù)碼管動(dòng)態(tài)顯示

Verilog HDL是一種硬件描述語言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言,用它可以表....

基于STEP-MXO2-C核心板設(shè)計(jì)機(jī)器人競賽通用軟硬件平臺

本設(shè)計(jì)采用STEP-MXO2-C核心板為控制板,設(shè)計(jì)了一款適用于各類機(jī)器人比賽的通用軟硬件平臺,30....

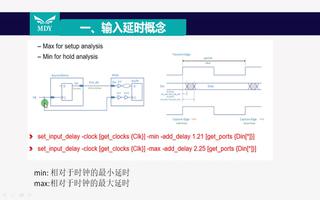

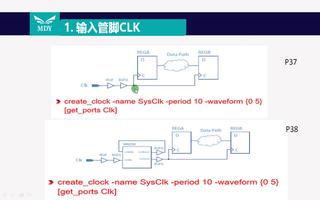

時(shí)序約束步驟:生成時(shí)鐘約束

差分時(shí)鐘是將數(shù)據(jù)從源傳送到目的地有兩種常用的電氣方法。一種方法使用“單端”發(fā)信號概念,它在發(fā)射機(jī)和接....

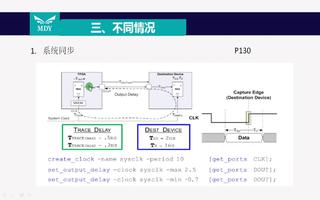

時(shí)序約束步驟:系統(tǒng)同步與源同步

針對普通時(shí)鐘系統(tǒng)存在著限制時(shí)鐘頻率的弊端,人們設(shè)計(jì)了一種新的時(shí)序系統(tǒng),稱之為源同步時(shí)序系統(tǒng)。它最大的....

時(shí)序約束:不需要檢查的路徑

時(shí)序表示動(dòng)態(tài)規(guī)?;蜻^程的時(shí)間演化。它們用于識別、建模和預(yù)測在離散時(shí)間間隔內(nèi)采樣的數(shù)據(jù)中的模式和行為。....

基于ZYNQ FPGA與PC的IP設(shè)計(jì)與驗(yàn)證方案(7)

Zynq-7000系列的可編程結(jié)構(gòu)經(jīng)定制可以最大化系統(tǒng)級性能,滿足特定應(yīng)用的各種需求。該套件提供了包....

基于ZYNQ FPGA與PC的IP設(shè)計(jì)與驗(yàn)證方案(6)

賽靈思可擴(kuò)展處理平臺芯片硬件的核心本質(zhì)就是將通用基礎(chǔ)雙ARMCortex-A9MPCore處理器系統(tǒng)....

基于ZYNQ FPGA與PC的IP設(shè)計(jì)與驗(yàn)證方案(5)

應(yīng)用開發(fā)人員利用可編程邏輯強(qiáng)大的并行處理能力,不僅可以解決多種不同信號處理應(yīng)用中的大量數(shù)據(jù)處理問題,....

基于ZYNQ FPGA與PC的IP設(shè)計(jì)與驗(yàn)證方案(4)

Zynq-7000嵌入式處理平臺系列的每款產(chǎn)品均采用帶有NEON及雙精度浮點(diǎn)引擎的雙核ARMCort....

基于ZYNQ FPGA與PC的IP設(shè)計(jì)與驗(yàn)證方案(3)

Zynq-7000系列的可編程邏輯完全基于賽靈思最新7系列FPGA架構(gòu)來設(shè)計(jì),可確保28nm系列器件....

基于ZYNQ FPGA與PC的IP設(shè)計(jì)與驗(yàn)證方案(2)

賽靈思公司(Xilinx)推出的行業(yè)第一個(gè)可擴(kuò)展處理平臺Zynq系列。旨在為視頻監(jiān)視、汽車駕駛員輔助....

基于ZYNQ FPGA與PC的IP設(shè)計(jì)與驗(yàn)證方案(1)

AXI總線是一種多通道傳輸總線,將地址、讀數(shù)據(jù)、寫數(shù)據(jù)、握手信號在不同的通道中發(fā)送,不同的訪問之間順....

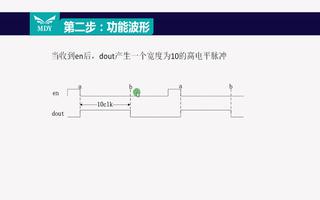

第一個(gè)設(shè)計(jì)思路講解:計(jì)數(shù)器架構(gòu)八步法講解

計(jì)數(shù)器是由基本的計(jì)數(shù)單元和一些控制門所組成,計(jì)數(shù)單元?jiǎng)t由一系列具有存儲(chǔ)信息功能的各類觸發(fā)器構(gòu)成,這些....

鋯石FPGA A4_Nano開發(fā)板視頻:HELLO FPGA之探索之謎

FPGA 的基本結(jié)構(gòu)包括可編程輸入輸出單元,可配置邏輯塊,數(shù)字時(shí)鐘管理模塊,嵌入式塊RAM,布線資源....

鋯石FPGA A4_Nano開發(fā)板視:PS/2外設(shè)IP核的應(yīng)用

IP核有三種不同的存在形式:HDL語言形式,網(wǎng)表形式、版圖形式。分別對應(yīng)我們常說的三類IP內(nèi)核:軟核....