Adam Taylor討論了使用Zynq?和Zynq UltraScale +?SoC開發(fā)圖像處理應....

Xilinx GTX(12.5 Gb / s)收發(fā)器與SFP +和10G背板一起運行����。

了解Avnet的模塊化MicroZed系統(tǒng)上的Anybus IP如何連接到商用PLC。

Xilinx慶祝三十年的行業(yè)第一

OmniTek總裁Mike Hodson在ARM TechCon 2013上展示了超高清電視成像處理....

采用Zynq?全可編程SoC實現(xiàn)的快速自然用戶界面眼圖跟蹤芯片技術

Virtex-7 GTH收發(fā)器與Altera Stratix-V GX器件Battle Kits D....

Bitmain生產(chǎn)比特幣采礦機以及最大的礦山和哈希率權衡平臺產(chǎn)品以及虛擬貨幣采礦業(yè)的服務����。

AXI USB 2.0設備IP概述

了解Xilinx的VC730 OTN測試開發(fā)平臺,適用于從1到400G的所有OTN應用的快速開發(fā)���。

該視頻展示了16nm FinFet器件的性能,并討論了Xilinx RFSoC技術如何減少占位面積和....

觀看Xilinx 28nm FPGA系列中第二款器件的演示 - 高性能Virtex-7 XV485T....

圖像處理與分析:UltraXR 4K波形監(jiān)視器/ VectorScope和Ultra 4k工具箱

這展示了DDR3內(nèi)存的Kintex-7 FPGA接口功能��。

了解Vivado中的Logic Debug功能�����,如何將邏輯調(diào)試IP添加到設計中�,以及如何使用Viva....

使用中速Kintex-7 325T FPGA演示DDR3控制器和接口,運行速度高于1866 Mbps....

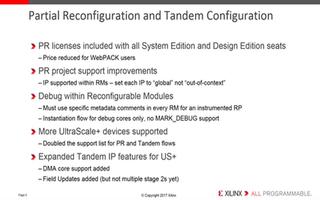

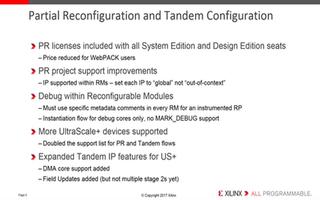

此視頻重點介紹了新的Vivado Design Suite 2017.1版本的增強功能�����,包括操作系統(tǒng)....

了解使用Vivado 2016.1中引入的增量編譯流程進行調(diào)試的好處����,以及在使用增量編譯實現(xiàn)時添加/....

用于異構計算的OpenCL標準為實現(xiàn)OpenCL標準的所有計算設備定義了基本編程模型����。

該視頻介紹....

在這段視頻中,Nick Difiore解釋了Xilinx FPGA的功能如何允許從機械顯示切換到電子....

了解協(xié)處理的價值����,Zynq-7000加速器一致性端口�����,使用協(xié)處理器加速器的方法以及協(xié)處理器設計實例的....

EyeTech數(shù)字系統(tǒng)總裁Robert Chappel在ARM TechCon 2013上展示了用于....

該視頻推出了一種電機控制設計流程���,支持在Mathworks MATLAB環(huán)境中設計和仿真高級模型。

該視頻演示展示了一個帶有多軸電機控制和EtherCAT網(wǎng)絡的集成驅(qū)動系統(tǒng)�。

QDesys實現(xiàn)的單....

了解如何創(chuàng)建一個異構多核系統(tǒng),該系統(tǒng)由處理系統(tǒng)上的ARM Cortex A9處理器和使用Vivado....

Vinay Singh�,高級產(chǎn)品經(jīng)理,使用Zynq-7000 All Programmable So....

了解適用于Zynq-7000 All Programmable SoC的模擬混合信號工具���。

此培訓....

Xilinx為Zynq-7000 SoC提供了一個穩(wěn)健而廣泛的支持基礎����,讓用戶基于Zynq的開發(fā)設計....

了解適用于Zynq-7000 All Programmable SoC的Windows Embedd....

ZedBoard(Zynq評估和開發(fā)委員會)

ZedBoard是一款完整的開發(fā)套件�����,適用于對使用X....