聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1664文章

22509瀏覽量

639540 -

控制器

+關(guān)注

關(guān)注

114文章

17886瀏覽量

195290 -

DDR3

+關(guān)注

關(guān)注

2文章

290瀏覽量

44285 -

賽靈思

+關(guān)注

關(guān)注

33文章

1798瀏覽量

133682

發(fā)布評論請先 登錄

相關(guān)推薦

熱點(diǎn)推薦

基于Xilinx K7 325t的千兆網(wǎng)UDP協(xié)議實(shí)現(xiàn)小記

基于xilinx k7 325t實(shí)現(xiàn)的千兆網(wǎng)udp協(xié)議,只需要設(shè)置好IP,端口,就可以直接給數(shù)據(jù),基本等同于透傳,可以不用管底層協(xié)議。

MAX17000:DDR2和DDR3內(nèi)存電源管理解決方案的卓越之選

的電源解決方案。Maxim Integrated的MAX17000脈沖寬度調(diào)制(PWM)控制器就是這樣一款出色的產(chǎn)品,它為DDR、DDR2和DDR3內(nèi)存提供了完整的電源解決方案。 文件

MAX17000A:DDR2和DDR3內(nèi)存電源管理的理想之選

MAX17000A:DDR2和DDR3內(nèi)存電源管理的理想之選 產(chǎn)品概述 在筆記本電腦DDR、DDR2和DDR3內(nèi)存的電源管理領(lǐng)域,Maxim

數(shù)據(jù)采集IO卡設(shè)計(jì)原理圖:136-KC705E增強(qiáng)版基于FMC接口的 Kintex-7 XC7K325T PCIeX8 接口卡

FMC子卡模塊, Kintex-7 XC7K325T板卡, 高速信號處理, 軟件無線電處理平臺, 數(shù)據(jù)采集IO卡

DDR3 SDRAM參考設(shè)計(jì)手冊

電子發(fā)燒友網(wǎng)站提供《DDR3 SDRAM參考設(shè)計(jì)手冊.pdf》資料免費(fèi)下載

發(fā)表于 11-05 17:04

?10次下載

【TES600】青翼凌云科技基于XC7K325T與TMS320C6678的通用信號處理平臺

Xilinx的Kintex-7系列FPGA XC7K325T作為協(xié)處理單元,具有1個(gè)FMC子卡接口,具有4路SFP+萬兆光纖接口,具有2路R

基于FPGA的DDR控制器設(shè)計(jì)

DDR控制協(xié)議

DDR3讀寫控制器主要用于生成片外存儲器DDR3 SDRAM進(jìn)行讀寫操作所需要的

發(fā)表于 10-21 14:30

基于DDR200T開發(fā)板的e203進(jìn)行DDR3擴(kuò)展

IP DDR3控制器 RISC-V

基于DDR200T開發(fā)板原理圖,找到所需要使用的DDR引腳,制成DDR.ucf文件方便在添加管腳約束時(shí)

發(fā)表于 10-21 12:43

FPGA搭建DDR控制模塊

DDR3讀寫控制器主要用于生成片外存儲器DDR3 SDRAM進(jìn)行讀寫操作所需要的時(shí)序,繼而實(shí)現(xiàn)對片外存儲器的讀寫訪問。由攝像頭采集得到的圖像

發(fā)表于 10-21 10:40

用FPGA實(shí)現(xiàn)DDR控制模塊介紹

DDR3讀寫控制器主要用于生成片外存儲器DDR3 SDRAM進(jìn)行讀寫操作所需要的時(shí)序,繼而實(shí)現(xiàn)對片外存儲器的讀寫訪問。由攝像頭采集得到的圖像

發(fā)表于 10-21 08:43

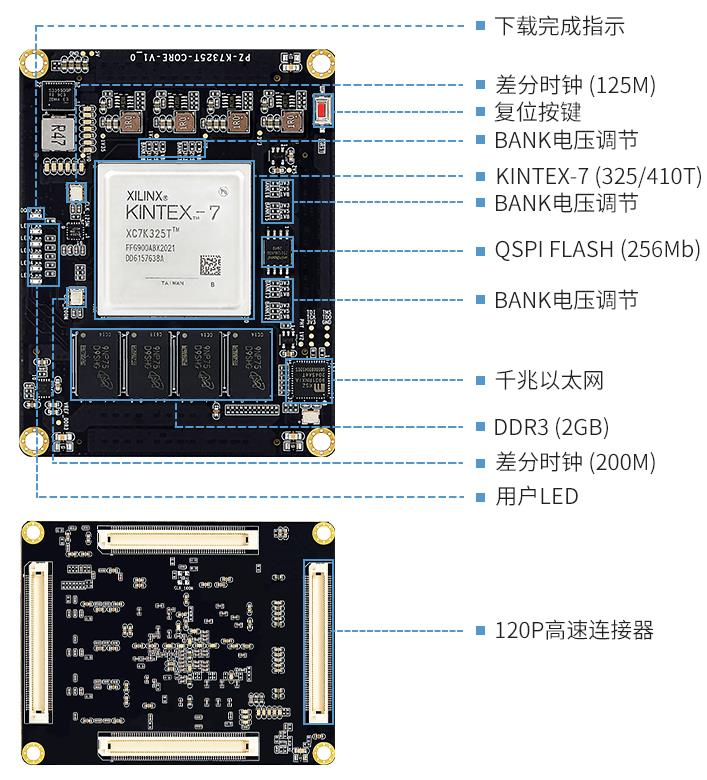

FPGA開發(fā)板—璞致 Kintex-7 系列核心板PZ-K7325T/PZ-K7410T 使用說明 XILINX核心板簡介

PZ-K7325T/PZ-K7410T核心板采用Xilinx Kintex-7系列FPGA為主控制器,提供326080/406720個(gè)邏輯單

【TES600G】青翼凌云科技基于JFM7K325T FPGA+FT-M6678 DSP的全國產(chǎn)化信號處理平臺

的Kintex-7系列FPGAJFM7K325T16作為協(xié)處理單元,具有1個(gè)FMC子卡接口,具有4路SFP+萬兆光纖接口,具有2路RJ45千兆以太網(wǎng)

AD設(shè)計(jì)DDR3時(shí)等長設(shè)計(jì)技巧

本文緊接著前一個(gè)文檔《AD設(shè)計(jì)DDR3時(shí)等長設(shè)計(jì)技巧-數(shù)據(jù)線等長 》。本文著重講解DDR地址線、控制信號線等長設(shè)計(jì),因?yàn)榈刂肪€、控制信號線有分支,SOC有可能帶有2片

發(fā)表于 07-29 16:14

?3次下載

AD設(shè)計(jì)DDR3時(shí)等長設(shè)計(jì)技巧

的講解數(shù)據(jù)線等長設(shè)計(jì)。? ? ? 在另一個(gè)文件《AD設(shè)計(jì)DDR3時(shí)等長設(shè)計(jì)技巧-地址線T型等長》中著重講解使用AD設(shè)計(jì)DDR地址線走線T型走線等長處理的方法和技巧。

發(fā)表于 07-28 16:33

?5次下載

國產(chǎn)化板卡設(shè)計(jì)原理圖:2330-基于FMC接口的JFM7K325T PCIeX4 3U PXIe接口卡

3U PXIe, FMQL45T900I, K7圖形圖像硬件加速器, PXIe接口卡, JFM7K325

Kintex-7 325T FPGA DDR3控制器和接口演示

Kintex-7 325T FPGA DDR3控制器和接口演示

評論