西門子數(shù)字化工業(yè)軟件推出新的Solido 設(shè)計環(huán)境軟件

新的IC設(shè)計和驗證解決方案結(jié)合了人工智能技術(shù)與云服務(wù)的可擴展性優(yōu)勢,旨在解決產(chǎn)品的復(fù)雜性,加快產(chǎn)品上....

西門子與SPIL合作為扇出型晶圓級封裝打造3D驗證工作流程

為了滿足市場對于高性能、低功耗、小尺寸IC的上揚需求,IC設(shè)計的封裝技術(shù)也變得日益復(fù)雜,2.5D和3....

西門子Calibre平臺通過N3E工藝認證

西門子數(shù)字化工業(yè)軟件日前在臺積電2023北美技術(shù)論壇上宣布一系列最新工藝認證。作為臺積電的長期合作伙....

使用硬件加速仿真進行有意義的功耗分析

功耗分析和優(yōu)化在最近幾年逐漸引起了人們的重視,大多數(shù) IC 設(shè)計團隊現(xiàn)在都會為了功耗管理在自己的流程....

各種類型CDC路徑中的毛刺問題

CDC 驗證不僅在 RTL 有必要,在門級也必不可少。在 RTL,重點是通過識別 CDC 結(jié)構(gòu)和方案....

適用于汽車市場的IC測試解決方案

乘用車中的電子部分持續(xù)快速增長,驅(qū)動這一現(xiàn)象的主要因素是乘用車中集成了各種先進安全功能。整個行業(yè)向全....

易于實現(xiàn)且全面的3D堆疊裸片器件測試方法

當裸片尺寸無法繼續(xù)擴大時,開發(fā)者開始考慮投入對 3D 堆疊裸片方法的研究??紤]用于 3D 封裝的高端....

在IC驗證的產(chǎn)品級工程中使用機器學(xué)習(xí)ML方法

由于半導(dǎo)體設(shè)計的復(fù)雜性、規(guī)模和任務(wù)關(guān)鍵型操作的增加,集成電路驗證要求也隨之大幅擴展。

一個典型設(shè)計的DFT組件

在本篇白皮書中,我們介紹了一個典型設(shè)計的 DFT 組件,并提出了多種可大幅改善 DFT 項目進度的智....

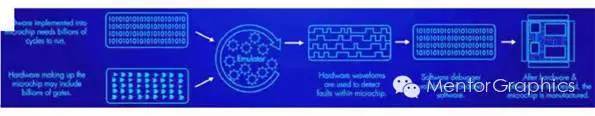

人工智能“入侵”芯片制造

現(xiàn)在幾乎所有的應(yīng)用包括5G、物聯(lián)網(wǎng)、汽車、數(shù)據(jù)中心等的實現(xiàn)與發(fā)展都建立在更高性能、更低功耗、更大算力....

FMEDA(失效模式影響和診斷分析) 安全機制的插入和驗證

FMEDA(失效模式影響和診斷分析)利用一系列安全機制來評估安全架構(gòu),并計算系統(tǒng)的安全性能。ISO ....

西門子推出Tessent Multi-die軟件解決方案 滿足多維設(shè)計的需求

西門子數(shù)字化工業(yè)軟件近日推出 Tessent Multi-die 軟件解決方案,旨在幫助客戶加快和簡....

西門子與聯(lián)華電子合作幫助客戶加快其集成產(chǎn)品設(shè)計的上市時間

西門子數(shù)字化工業(yè)軟件近日與半導(dǎo)體晶圓制造大廠聯(lián)華電子 (UMC) 合作,面向聯(lián)華電子的晶圓堆疊 (w....

在流片前驗證中如何測量功耗 執(zhí)行功耗分析的步驟是什么

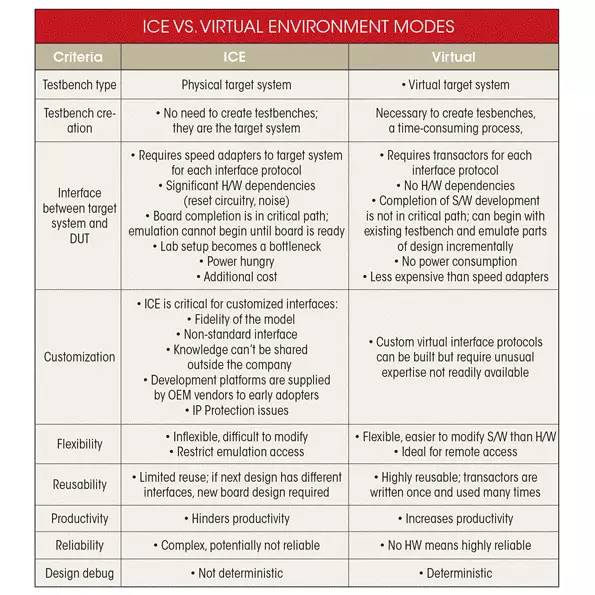

一般來說,功耗測量是在門級進行,通過由回歸向量組成的驗證平臺執(zhí)行 DUT,然后跟蹤 DUT 的開關(guān)活....

西門子EDA助力數(shù)字化創(chuàng)新 賦能產(chǎn)業(yè)可持續(xù)發(fā)展

伴隨5G、汽車電子、人工智能及物聯(lián)網(wǎng)等技術(shù)的不斷發(fā)展,全球半導(dǎo)體產(chǎn)業(yè)需求也保持持續(xù)增長態(tài)勢,根據(jù)半導(dǎo)....

十種常見的器件噪聲分析錯誤

器件噪聲的影響在納米級 CMOS 工藝中極為關(guān)鍵,因為它在根本上制約了許多 45 nm 及以下工藝電....

西門子EDA產(chǎn)品OneSpin助力實現(xiàn)精確的驗證覆蓋率指標

近日,西門子數(shù)字化工業(yè)軟件與總部位于倫敦的Azini Capital簽訂了收購OneSpin Sol....

回顧西門子EDA研討會 看破解先進制程最新挑戰(zhàn)

隨著AI時代的到來,市場上對大數(shù)據(jù)處理速度的需求越來越高。眾所周知,工藝制程的進步是實現(xiàn)高性能計算最....

MATLAB中的振動分析與信號處理分析

模態(tài)分析主要研究頻率域內(nèi)系統(tǒng)動態(tài)特性。 通過模態(tài)分析方法搞清楚了結(jié)構(gòu)物在某一易受影響的頻率范圍內(nèi)的各....

總結(jié)一些高效地定制和完善車輛動力學(xué)模型的經(jīng)驗

上期的強強對話中來自同濟大學(xué) DIAN Racing 車隊的周曉同學(xué)給我們分享了如何繞過車輛電氣系統(tǒng)....

簡述MATLAB中傳統(tǒng)信號如何處理

振動分析在工程領(lǐng)域很常見,汽車中的 NVH,風機的模態(tài)分析,塔架、葉片等機械件的振動頻率分析,發(fā)電機....

言驗證通常構(gòu)成整個驗證IP開發(fā)周期不可或缺的一部分

斷言是一種條件語句,通過標記錯誤繼而捕獲錯誤來指示設(shè)計的不正確行為。斷言用于驗證處于不同生命周期階段....

關(guān)于五大物聯(lián)網(wǎng)和網(wǎng)絡(luò)驗證挑戰(zhàn)的分析和介紹

例如,為滿足需求而產(chǎn)生的大量網(wǎng)絡(luò)配置迫使較新網(wǎng)絡(luò)芯片的開發(fā)人員不得不將數(shù)以千計的以太網(wǎng)端口置于單個S....

關(guān)于UVM SystemVerilog驗證IP庫的性能分析和介紹

驗證IP旨在通過為常見接口、協(xié)議和架構(gòu)提供可復(fù)用構(gòu)建模塊來幫助工程師減少構(gòu)建測試平臺所花費的時間。M....

關(guān)于可穿戴醫(yī)療設(shè)備的性能分析和介紹

可穿戴醫(yī)療設(shè)備的電池續(xù)航時間顯然是一大關(guān)鍵要素。對于人們隨身攜帶或佩戴的任何設(shè)備而言,重量始終都是一....

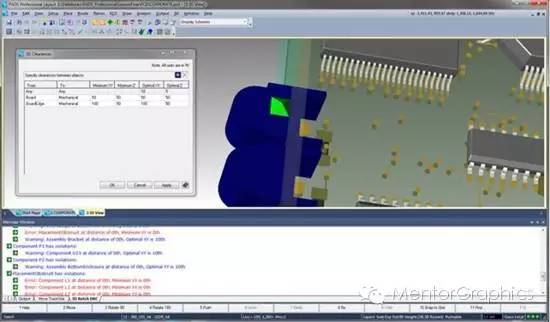

關(guān)于設(shè)計效率策略的研究和分享

總之,使用虛擬原型,包括信號和電源完整性、熱分析、DFM和三維驗證,現(xiàn)在對于減少設(shè)計迭代、滿足緊湊的....

關(guān)于FinFET技術(shù)中的電路設(shè)計的分析和介紹

通過這些EDA創(chuàng)新,如果你是即將采用FinFET工藝的數(shù)字設(shè)計人員且最近的節(jié)點是20nm,那么Fin....