VCSEL相較于傳統(tǒng)的邊射型雷射而言�,另一項(xiàng)重要的區(qū)分在于VCSBL 具有很短的雷射共振腔。

進(jìn)一步考量到 DBR 的設(shè)計(jì)時(shí)����,雖然界面平整的異質(zhì)結(jié)構(gòu)可以提供較大而明顯的折射率差異以達(dá)到較高的 D....

相較于傳統(tǒng)邊射型半導(dǎo)體雷射的發(fā)展,垂直共握腔面射型雷射(VCSEL)的設(shè)計(jì)概念直到1979年首先被I....

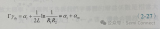

共振腔中雷射光來回(round trip)振蕩后保持光學(xué)自再現(xiàn)(self-consistency)的....

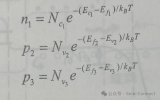

在半導(dǎo)體中����,光子的放射是由電子和電洞借由垂直躍遷所達(dá)成的,我們可以把具有相同k值的電子一電洞看成一種....

一個(gè)基本的半導(dǎo)體雷射如圖2-1所示��,包含了兩個(gè)平行劈裂鏡面組成的共振腔���,稱為Fabry-Perot?....

早期面射型雷射由于半導(dǎo)體磊晶技術(shù)簡(jiǎn)在發(fā)展初期階段��,因此還無法直接成長(zhǎng)反射率符合雷射操作需求的全磊晶導(dǎo)....

早期所謂的面射型雷射(surface emitting laser, EBL)本質(zhì)上仍然是邊射型雷射....

LASER是“l(fā)ight amplification by stimulated emission ....

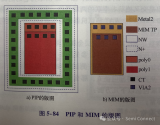

CMOS 工藝技術(shù)平臺(tái)的電容包括 MIM 和 PIP (Poly Insulator Poly)����。P....

CMOS 工藝平臺(tái)的金屬方塊電阻的測(cè)試結(jié)構(gòu)包含該平臺(tái)的所有金屬層���,例如如果該平臺(tái)使用五層金屬層���,那么....

CMOS工藝平臺(tái)的Poly 方塊電阻有四種類型的電阻��,它們分別是n型金屬硅化物 Poly 方塊電阻�����、....

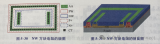

圖5-34所示為PW方塊電阻的版圖�����,圖5-35所示為它的剖面圖。PW方塊電阻是通過DNW 隔離襯底(....

CMOS 工藝技術(shù)平臺(tái)的方塊電阻的測(cè)試結(jié)構(gòu)是NW方塊電阻���、PW方塊電阻�����、Poly 方塊電阻����、AA 方....

雖然 WAT測(cè)試類型非常多�,不過業(yè)界對(duì)于 WAT測(cè)試類型都有一個(gè)明確的要求,就是包括該工藝技術(shù)平臺(tái)所....

WAT是英文 Wafer Acceptance Test 的縮寫���,意思是晶圓接受測(cè)試�����,業(yè)界也稱WAT....

頂層金屬 AI工藝是指形成頂層金屬 AI 互連線����。因?yàn)?Cu很容易在空氣中氧化,形成疏松的氧化銅���,而....

IMD4 工藝是形成 TMV (Top Metal VIA��,頂層金屬通孔)的介質(zhì)隔離材料�����,同時(shí)IMD....

IMD3工藝包括 IMD3a工藝和IMD3b工藝����。IMD3a 工藝是形成 VIA2 的介質(zhì)隔離材料���,....

接觸孔工藝是指在 ILD 介質(zhì)層上形成很多細(xì)小的垂直通孔�,它是器件與第一層金屬層的連接通道�����。通孔的填....

IMD1工藝是指在第一層金屬之間的介質(zhì)隔離材料。IMD1的材料是 ULK (Ultra Low K)....

金屬層1工藝是指形成第一層金屬互連線�����,第一層金屬互連線的目的是實(shí)現(xiàn)把不同區(qū)域的接觸孔連起來�����,以及把不....

ILD 工藝是指在器件與第一層金屬之間形成的介質(zhì)材料����,形成電性隔離�����。ILD介質(zhì)層可以有效地隔離金屬互....

Salicide 工藝是指在沒有氧化物覆蓋的襯底硅和多晶硅上形成金屬硅化物����,從而得到低阻的有源區(qū)和多....

與亞微米工藝類似,源漏離子注入工藝是指形成器件的源漏有源區(qū)重?fù)诫s的工藝���,降低器件有源區(qū)的串聯(lián)電阻��,提....

與亞微米工藝類似�����,側(cè)墻工藝是指形成環(huán)繞多晶硅的氧化介質(zhì)層�,從而保護(hù)LDD 結(jié)構(gòu),防止重?fù)诫s的源漏離子....

與亞微米工藝類似����,多晶硅柵工藝是指形成 MOS器件的多晶硅柵極,柵極的作用是控制器件的關(guān)閉或者導(dǎo)通�。....

與亞微米工藝類似,柵氧化層工藝是通過熱氧化形成高質(zhì)量的柵氧化層�����,它的熱穩(wěn)定性和界面態(tài)都非常好�。

與亞微米工藝類似,雙阱工藝是指形成NW和PW的工藝����,NMOS 是制造在PW里的,PMOS是制造在NW....

STI 隔離工藝是指利用氧化硅填充溝槽���,在器件有源區(qū)之間嵌入很厚的氧化物����,從而形成器件之間的隔離。利....