半導(dǎo)體封裝框架的外部結(jié)構(gòu)設(shè)計(jì)

封裝框架的外部結(jié)構(gòu)設(shè)計(jì),核心包含聯(lián)筋(Dambar)與假腳(False leads)兩大關(guān)鍵部分,以....

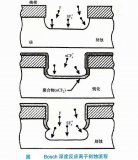

集成電路制造中Bosch工藝的關(guān)鍵作用和流程步驟

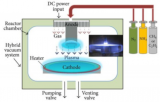

Bosch工藝,又稱交替?zhèn)缺阝g化深層硅蝕刻工藝,是一種在半導(dǎo)體制造中用于刻蝕硅片上特定材料層的先進(jìn)技....

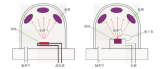

詳解NMOS晶體管的工作過(guò)程

在每一顆芯片的內(nèi)部,數(shù)十億個(gè)晶體管如同高速開(kāi)合的微型水閘,構(gòu)成數(shù)字世界的最小邏輯單元。以NMOS為例....

淺談芯片驗(yàn)證方法的演進(jìn)過(guò)程

回溯 20 世紀(jì) 90 年代,當(dāng)時(shí)行業(yè)內(nèi)接觸的芯片主要包括 Z80、8031、8080/8086 等....

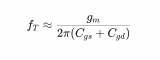

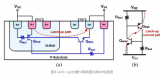

運(yùn)算放大器的核心組成與典型結(jié)構(gòu)

運(yùn)算放大器是模擬電路與混合信號(hào)電路的核心基礎(chǔ)模塊,其性能直接決定電子系統(tǒng)的信號(hào)處理精度與穩(wěn)定性。掌握....

晶圓接受測(cè)試的具體內(nèi)容與重要作用

在智能手機(jī)、電腦和自動(dòng)駕駛汽車等高科技產(chǎn)品的背后,隱藏著一項(xiàng)至關(guān)重要的半導(dǎo)體制造技術(shù)——晶圓接受測(cè)試....

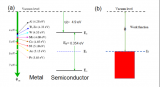

功函數(shù)在芯片制造中的核心作用

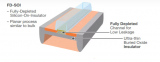

在我們手中的智能手機(jī)和電腦核心,躺著一塊精密的芯片。芯片的核心,是數(shù)十億個(gè)名為“晶體管”的微觀開(kāi)關(guān)。....

芯片制造檢驗(yàn)工藝中的全數(shù)檢查

在IC芯片制造的檢驗(yàn)工藝中,全數(shù)檢查原則貫穿于關(guān)鍵工序的缺陷篩查,而老化測(cè)試作為可靠性驗(yàn)證的核心手段....

半導(dǎo)體制造中的多層芯片封裝技術(shù)

在半導(dǎo)體封裝領(lǐng)域,已知合格芯片(KGD)作為多層芯片封裝(MCP)的核心支撐單元,其價(jià)值在于通過(guò)封裝....

如何理解MOSFET器件溝道電荷分配原則

在模擬集成電路設(shè)計(jì)中,精確的MOSFET模型是確保電路性能預(yù)測(cè)準(zhǔn)確性的基石。而溝道電荷分配原則,正是....

離子注入工藝中的常見(jiàn)問(wèn)題及解決方案

在集成電路制造的離子注入工藝中,完成離子注入與退火處理后,需對(duì)注入結(jié)果進(jìn)行嚴(yán)格的質(zhì)量檢查,以確保摻雜....

金屬淀積工藝的核心類型與技術(shù)原理

在集成電路制造中,金屬淀積工藝是形成導(dǎo)電結(jié)構(gòu)(如互連線、柵電極、接觸塞)的關(guān)鍵環(huán)節(jié),主要包括蒸發(fā)、濺....

PN結(jié)的形成機(jī)制和偏置特性

PN 結(jié)是構(gòu)成二極管、雙極型晶體管、MOS 晶體管等各類半導(dǎo)體器件的核心結(jié)構(gòu),其本質(zhì)是 p 型半導(dǎo)體....

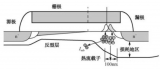

化學(xué)氣相淀積工藝的常見(jiàn)類型和技術(shù)原理

APCVD 的反應(yīng)腔結(jié)構(gòu)如圖所示,系統(tǒng)通過(guò)專用傳送裝置實(shí)現(xiàn)硅片的自動(dòng)化運(yùn)送,反應(yīng)氣體從反應(yīng)腔中部區(qū)域....

化學(xué)氣相淀積工藝的核心特性和系統(tǒng)分類

化學(xué)氣相淀積(CVD)是借助混合氣體發(fā)生化學(xué)反應(yīng),在硅片表面沉積一層固體薄膜的核心工藝。在集成電路制....

詳解半導(dǎo)體制造中的回流技術(shù)

玻璃回流(reflow)技術(shù)是通過(guò)升溫加熱雜氧化硅,使其產(chǎn)生流動(dòng)特性的工藝,常見(jiàn)的回流處理對(duì)象包含硼....

半導(dǎo)體中的合金制備技術(shù)詳解

合金本質(zhì)是金屬與其他金屬或非金屬經(jīng)混合熔化、冷卻凝固后形成的具有金屬性質(zhì)的固體產(chǎn)物,而在集成電路工藝....

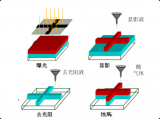

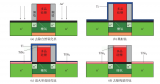

什么是晶圓切割與框架內(nèi)貼片

在半導(dǎo)體制造的精密工藝鏈條中,芯片切割作為晶圓級(jí)封裝的關(guān)鍵環(huán)節(jié),其技術(shù)演進(jìn)與設(shè)備精度直接關(guān)系到芯片良....

芯片制造過(guò)程中的布線技術(shù)

從鋁到銅,再到釕與銠,半導(dǎo)體布線技術(shù)的每一次革新,都是芯片性能躍升的關(guān)鍵引擎。隨著制程進(jìn)入2nm時(shí)代....

晶圓制造過(guò)程中的摻雜技術(shù)

在超高純度晶圓制造過(guò)程中,盡管晶圓本身需達(dá)到11個(gè)9(99.999999999%)以上的純度標(biāo)準(zhǔn)以維....

三維集成電路與晶圓級(jí)3D集成介紹

微電子技術(shù)的演進(jìn)始終圍繞微型化、高效性、集成度與低成本四大核心驅(qū)動(dòng)力展開(kāi),封裝技術(shù)亦隨之從傳統(tǒng)TSO....

CMOS集成電路中閂鎖效應(yīng)的產(chǎn)生與防護(hù)

閂鎖效應(yīng)(Latch-up)是CMOS集成電路中一種危險(xiǎn)的寄生效應(yīng),可能導(dǎo)致芯片瞬間失效甚至永久燒毀....

淺談三維集成封裝技術(shù)的演進(jìn)

在半導(dǎo)體封裝領(lǐng)域,堆疊技術(shù)作為推動(dòng)高集成度與小型化的核心趨勢(shì),正通過(guò)垂直堆疊芯片或封裝實(shí)現(xiàn)更緊湊的封....

熱載流子注入效應(yīng)對(duì)芯片有什么危害

熱載流子注入效應(yīng)(Hot Carrier Inject, HCI)是半導(dǎo)體器件(如晶體管)工作時(shí),高....