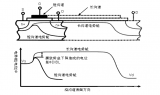

拋光設(shè)備的核心自動化配置要求和關(guān)鍵工藝參數(shù)

在半導(dǎo)體器件規(guī)?;慨a(chǎn)過程中,拋光設(shè)備的自動化水平直接決定生產(chǎn)效率、工藝穩(wěn)定性與作業(yè)安全性,需同時滿....

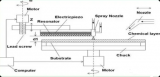

半導(dǎo)體制造中晶圓清洗設(shè)備介紹

在半導(dǎo)體制造過程中,晶圓清洗是一道至關(guān)重要的工序。晶圓經(jīng)切割后,表面常附著大量由聚合物、光致抗蝕劑及....

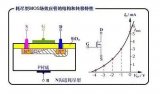

深度解讀晶體管的轉(zhuǎn)移特性曲線

本文介紹了晶體管轉(zhuǎn)移特性曲線及其核心參數(shù)的意義。曲線描述了柵壓控制漏極電流的過程,涵蓋關(guān)斷、亞閾值與....

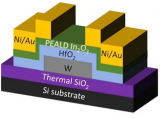

MIT團隊提出一種垂直集成的BEOL堆疊架構(gòu)

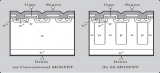

近期發(fā)現(xiàn),通過在傳統(tǒng)CMOS芯片的后端工藝(BEOL)層添加額外的有源器件層,可將原本僅用于布線的區(qū)....

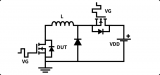

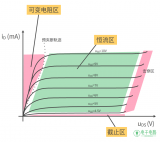

晶體管輸出特性曲線的構(gòu)成與核心區(qū)域

晶體管的輸出特性曲線是半導(dǎo)體器件物理與芯片電路設(shè)計之間最關(guān)鍵的橋梁。這張圖表描繪了在固定柵極電壓下,....

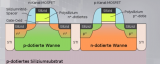

超結(jié)MOSFET的基本結(jié)構(gòu)與工作原理

超結(jié)MOSFET(Super-Junction MOSFET,簡稱SJ-MOS)是一種在高壓功率半導(dǎo)....

SOI晶圓片的結(jié)構(gòu)特性及表征技術(shù)

SOI晶圓片結(jié)構(gòu)特性由硅層厚度、BOX層厚度、Si-SiO?界面狀態(tài)及薄膜缺陷與應(yīng)力分布共同決定,其....

淺談SOI晶圓制造技術(shù)的四大成熟工藝體系

SOI晶圓片制造技術(shù)作為半導(dǎo)體領(lǐng)域的核心分支,歷經(jīng)五十年技術(shù)沉淀與產(chǎn)業(yè)迭代,已形成以SIMOX、BS....

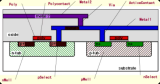

集成電路版圖設(shè)計的核心組成與關(guān)鍵步驟

在集成電路設(shè)計中,版圖(Layout)是芯片設(shè)計的核心環(huán)節(jié)之一,指芯片電路的物理實現(xiàn)圖。它描述了電路....

不同維度下半導(dǎo)體集成電路的分類體系

半導(dǎo)體集成電路的分類體系基于集成度、功能特性、器件結(jié)構(gòu)及應(yīng)用場景等多維度構(gòu)建,歷經(jīng)數(shù)十年發(fā)展已形成多....

半導(dǎo)體的能帶結(jié)構(gòu)與核心摻雜工藝詳解

本文將聚焦半導(dǎo)體的能帶結(jié)構(gòu)、核心摻雜工藝,以及半導(dǎo)體二極管的工作原理——這些是理解復(fù)雜半導(dǎo)體器件的基....

半導(dǎo)體封裝框架的外部結(jié)構(gòu)設(shè)計

封裝框架的外部結(jié)構(gòu)設(shè)計,核心包含聯(lián)筋(Dambar)與假腳(False leads)兩大關(guān)鍵部分,以....

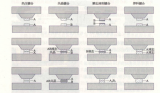

集成電路制造中Bosch工藝的關(guān)鍵作用和流程步驟

Bosch工藝,又稱交替?zhèn)缺阝g化深層硅蝕刻工藝,是一種在半導(dǎo)體制造中用于刻蝕硅片上特定材料層的先進技....